In order to manage complex and big data and perform high performance computing we have proposed a Supercomputing Research Group (SRG).

UCERD Supercomputing Research Group is one of the largest supercomputing research center in Pakistan.

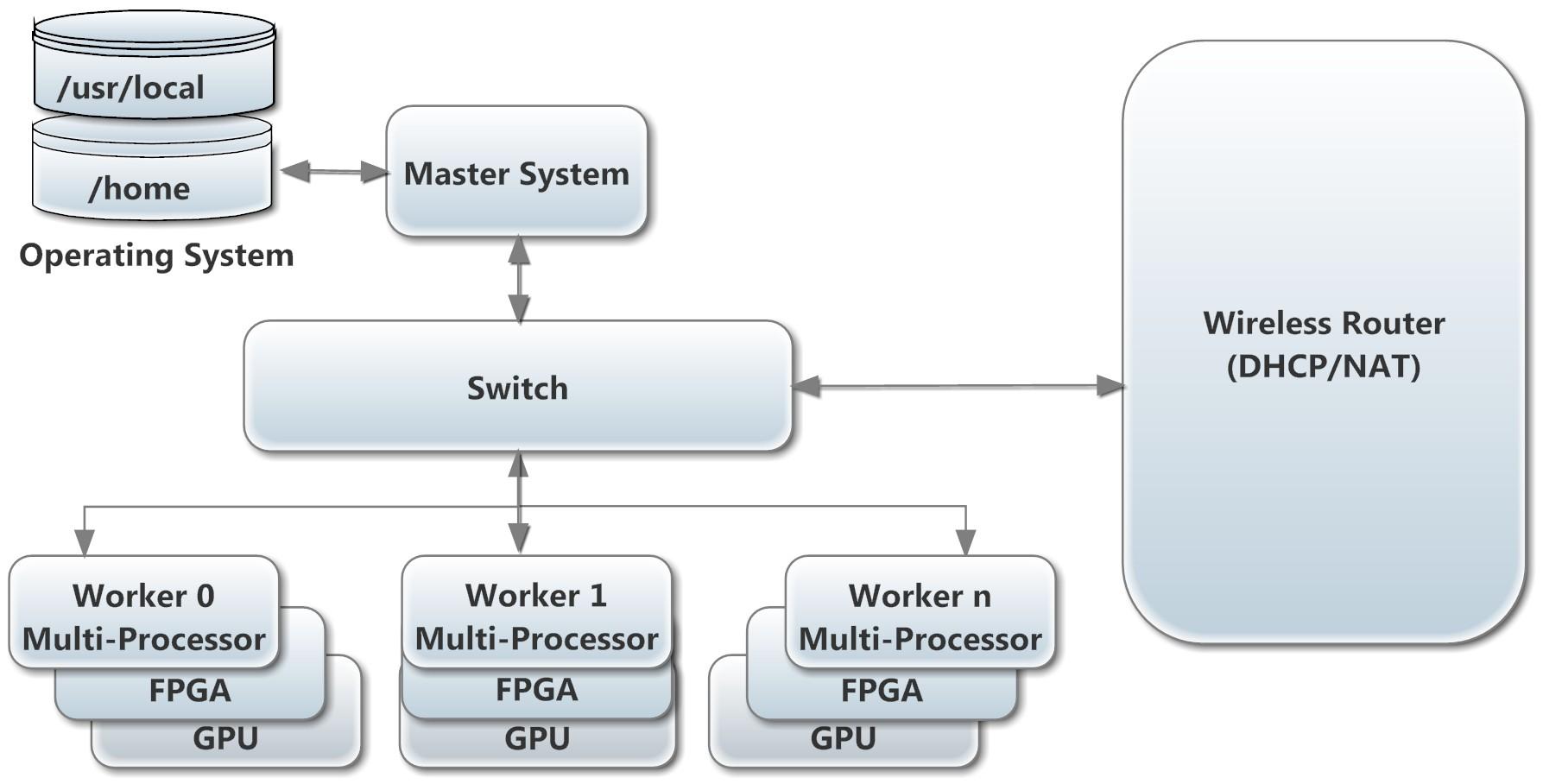

The Supercomputing Reserach Group (ScRG) can work on research, industry and defence projects, including big data processing, signal processing, and low power computing. The SRG targest different high performance architectures for super computing. A generic block diagram of target design is shown in Figure.

The proposed architecture uses FPGAs based accelerators, DSP, GPU and RISC multi-core system. A High level synthesis tool is used to program FPGA accelerators for specific applications. These dedicated accelerators have low footprint and low power consumption and provide high performance. SIMD architecture uses DSPs and the CUDA Tesla, Fermi, etc. architectures," the GPU Computing Modules. Low power ARM and high performance x86 multi-core processor systems are also used in the Super-Cluster system which allows system to execute most of the generic C/C++ applications. The proposed system is ideal for seismic processing, biochemistry simulations, weather and climate modeling, signal processing, computational finance, CAE, CFD and data analytics.

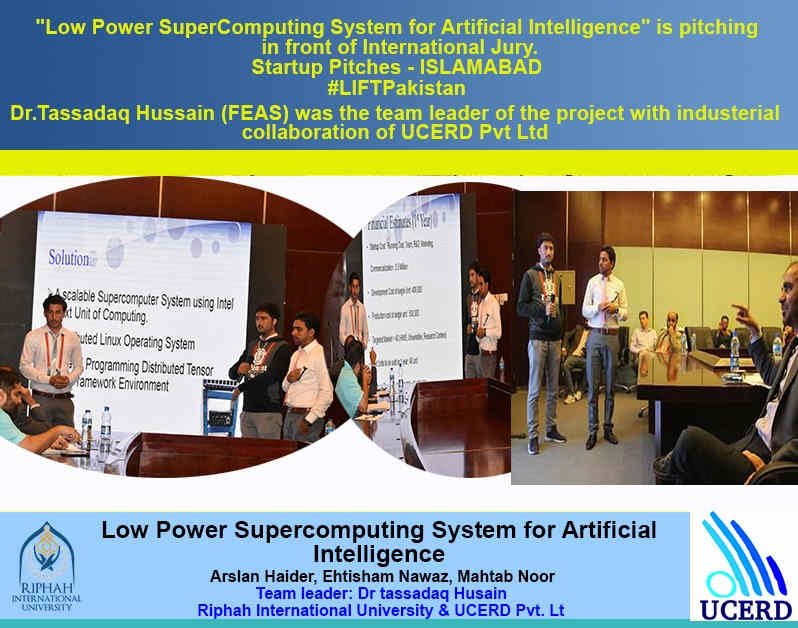

Case Study of Supercomputing in Pakistan

The main objectives of the Supercomputing Research Group:

Provide a low-power low-cost super computing resources to work out of academic, research and defence project.

Generate a team of collaborations for faculty, post-graduate students, specialists, scientists and technical resources working on high performance computing projects and initiatives.

Propose and Develop low-power low-cost embedded and heterogeneous system architectures for compute intensive applications.

The SRG targets three types of Super-Cluster architectures which are the Low Power Low-Cost Super-Cluster, the Transitional Performance Super-Cluster and the High-Performance Super-Cluster. The SRG is categorized into the following subsections: Target Applications, Programming Models and Toolkits, Supported Operating System, and Performacne Cost and Power.

UCERD Supercomputing Research Group is one of the largest supercomputing research center in Pakistan.

The Supercomputing Reserach Group (ScRG) can work on research, industry and defence projects, including big data processing, signal processing, and low power computing. The SRG targest different high performance architectures for super computing. A generic block diagram of target design is shown in Figure.

The proposed architecture uses FPGAs based accelerators, DSP, GPU and RISC multi-core system. A High level synthesis tool is used to program FPGA accelerators for specific applications. These dedicated accelerators have low footprint and low power consumption and provide high performance. SIMD architecture uses DSPs and the CUDA Tesla, Fermi, etc. architectures," the GPU Computing Modules. Low power ARM and high performance x86 multi-core processor systems are also used in the Super-Cluster system which allows system to execute most of the generic C/C++ applications. The proposed system is ideal for seismic processing, biochemistry simulations, weather and climate modeling, signal processing, computational finance, CAE, CFD and data analytics.

Case Study of Supercomputing in Pakistan

The main objectives of the Supercomputing Research Group:

Provide a low-power low-cost super computing resources to work out of academic, research and defence project.

Generate a team of collaborations for faculty, post-graduate students, specialists, scientists and technical resources working on high performance computing projects and initiatives.

Propose and Develop low-power low-cost embedded and heterogeneous system architectures for compute intensive applications.

The SRG targets three types of Super-Cluster architectures which are the Low Power Low-Cost Super-Cluster, the Transitional Performance Super-Cluster and the High-Performance Super-Cluster. The SRG is categorized into the following subsections: Target Applications, Programming Models and Toolkits, Supported Operating System, and Performacne Cost and Power.

[1] Authors: Wasim, Akram.; Tassadaq Hussain; Eduard Ayguade.

Title: FPGA and ARM Processor based Supercomputing

Conference: 2018 International Conference on Computing, Mathematics and Engineering Technologies – iCoMET 2018.

Publisher: IEEE Xplorer.

ISBN: 978-1-5386-1370-2.

[2] Memory Resources Aware Run-Time Automated Scheduling Policy for Multi-core Systems Authors Tassadaq Hussain Publication date 2017/12/16 Journal Microprocessors and Microsystems Publisher Elsevier

[3] Memory Resources Aware Run-Time Automated Scheduling Policy for Multi-core Systems, Tassadaq Hussain. ScienceDirect Microprocessors and Microsystems 2017. ISSN: 0141-9331 IF: 1.025

[4] ViPS: A Novel Visual Processing System Architecture for Medical Imaging: Tassadaq Hussain, ScienceDirect Biomedical Signal Processing and Control, ISSN: 1746-8094. IF: 2.214

[5] Formation of pn-junction with stable n-doping in graphene field effect transistors using e-beam irradiation. Muhammad Zahir Iqbal, Nadia Anwar, Salma Siddique, Muhammad Waqas Iqbal, Tassadaq Hussain. Journal of Optical Materials 2017, ISSN: 0925-3467 IF: 2.238

[6] A Novel Hardware Support for Heterogeneous Multi-core Memory System : Tassadaq Hussain, ScienceDirect Journal of Parallel and Distributed Computing 2016, ISSN: 0743-7315. IF: 1.930

[7] PMSS: A Programmable Memory System and Scheduler for Regular Memory Patterns: Tassadaq Hussain, Eduard Ayguade and Amna Haider. ScienceDirect Journal of Parallel and Distributed Computing 2014. ISSN: 0743-7315 IF:1.930

[8] AMC: Advanced Multi-core Controller: Tassadaq Hussain, Amna Haider, Shakaib Arsalan and Eduard Ayguade. ScienceDirect Journal of Parallel Computing 2014. ISSN: 0167-8191 IF: 1.511

[9] Memory Controller for Vector Processor: Tassadaq Hussain, Springer Journal of VLSI Signal Processing Systems for Signal, Image, and Video Technology 2016. ISSN: 1939-8018 IF: 0.893

[10] HMMC: A Memory Controller for Heterogeneous Multi-core System, Tassadaq Hussain. ScienceDirect Microprocessors and Microsystems 2015. ISSN: 0141-9331 IF: 1.025

[11] PGC: a pattern-based graphics controller: Tassadaq Hussain and Amna Haider. Int. J. Circuits and Architecture Design 2014.

Title: FPGA and ARM Processor based Supercomputing

Conference: 2018 International Conference on Computing, Mathematics and Engineering Technologies – iCoMET 2018.

Publisher: IEEE Xplorer.

ISBN: 978-1-5386-1370-2.

[2] Memory Resources Aware Run-Time Automated Scheduling Policy for Multi-core Systems Authors Tassadaq Hussain Publication date 2017/12/16 Journal Microprocessors and Microsystems Publisher Elsevier

[3] Memory Resources Aware Run-Time Automated Scheduling Policy for Multi-core Systems, Tassadaq Hussain. ScienceDirect Microprocessors and Microsystems 2017. ISSN: 0141-9331 IF: 1.025

[4] ViPS: A Novel Visual Processing System Architecture for Medical Imaging: Tassadaq Hussain, ScienceDirect Biomedical Signal Processing and Control, ISSN: 1746-8094. IF: 2.214

[5] Formation of pn-junction with stable n-doping in graphene field effect transistors using e-beam irradiation. Muhammad Zahir Iqbal, Nadia Anwar, Salma Siddique, Muhammad Waqas Iqbal, Tassadaq Hussain. Journal of Optical Materials 2017, ISSN: 0925-3467 IF: 2.238

[6] A Novel Hardware Support for Heterogeneous Multi-core Memory System : Tassadaq Hussain, ScienceDirect Journal of Parallel and Distributed Computing 2016, ISSN: 0743-7315. IF: 1.930

[7] PMSS: A Programmable Memory System and Scheduler for Regular Memory Patterns: Tassadaq Hussain, Eduard Ayguade and Amna Haider. ScienceDirect Journal of Parallel and Distributed Computing 2014. ISSN: 0743-7315 IF:1.930

[8] AMC: Advanced Multi-core Controller: Tassadaq Hussain, Amna Haider, Shakaib Arsalan and Eduard Ayguade. ScienceDirect Journal of Parallel Computing 2014. ISSN: 0167-8191 IF: 1.511

[9] Memory Controller for Vector Processor: Tassadaq Hussain, Springer Journal of VLSI Signal Processing Systems for Signal, Image, and Video Technology 2016. ISSN: 1939-8018 IF: 0.893

[10] HMMC: A Memory Controller for Heterogeneous Multi-core System, Tassadaq Hussain. ScienceDirect Microprocessors and Microsystems 2015. ISSN: 0141-9331 IF: 1.025

[11] PGC: a pattern-based graphics controller: Tassadaq Hussain and Amna Haider. Int. J. Circuits and Architecture Design 2014.

Supercomputing Research Group (ScRG)

UCERD Rawalpindi

Supercomputing Center

UCERD Murree

Supercomputing Research Group (ScRG) is a leading supercomputing research group in Pakistan that provides hardware/software solution for high performance computing problems. The ScRG provides novel ideas related to supercomputing hardware architecture, parallel programming enviroment and HPC applications.